# mercury

# DRF5580

3U VPX SOSA Aligned 4-Channel A/D and D/A Board based on the Intel<sup>®</sup> Agilex<sup>®</sup> 9 Direct RF-Series

Developed in alignment with the SOSA Technical Standard

- High-bandwidth data streaming

- Waveform signal generator

- Communication receiver and transmitter

- Electronic Warfare transponder

- Analog I/O for digital recording and playback

- Sensor interfaces

The DRF5580 is a high-performance, SOSA™ aligned 3U Open VPX board based on the Intel Agilex 9 Direct RF-Series. Four 64 GSPS A/D and D/A converters are integrated into the Agilex 9's multiprocessor architecture, creating a multichannel data conversion and processing solution on a single chip. The DRF5580 brings Agilex 9 performance to 3U VPX with a complete system on a board.

Complementing the Agilex 9's on-chip resources are the DRF5580's sophisticated clocking section for multichannel and multiboard synchronization, a modular front end for RF input and output, 16 GBytes of DDR4, a 10 GigE interface, a 40 GigE interface, a gigabit serial optical interface capable of supporting dual 100 GigE connections and general-purpose serial and parallel signal paths to the FPGA.

#### **FEATURES**

- Developed in alignment with the SOSA<sup>™</sup> Technical Standard

- Incorporates Intel Agilex 9 Direct RF AGRW014

- 16 GB of DDR4 SDRAM

- 10 GigE Interface

- 40 GigE Interface

- Optional VITA 67.3C optical interface for gigabit serial communication

- Dual 100 GigE UDP interface

- Compatible with several VITA standards including: VITA 46, VITA 48, VITA 67.3C, and VITA 65 (OpenVPX™ System Specification)

- Ruggedized and conduction-cooled

- Unique system-on-module design enables migration to other form factors

- Board Support Package (BSP) for software development

- FPGA Design Kit (FDK) for custom IP development

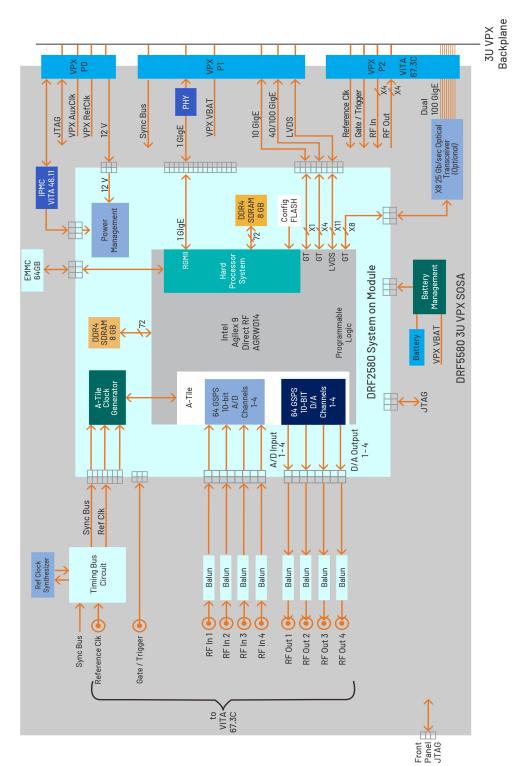

## DRF5580 BLOCK DIAGRAM

Click on a block for more information.

#### **BOARD ARCHITECTURE**

The DRF5580 board design places the Agilex 9 as the cornerstone of the architecture. All control and data paths are accessible by the programmable logic and processing system. A full suite of Mercury-developed IP and software functions utilize this architecture to provide data capture, waveform generation, and interface solutions for many of the most common application requirements.

#### A/D CONVERTER STAGE

The analog interface accepts analog RF inputs on four coax connectors located within a VITA 67.3C connector. These inputs are transformer-coupled into the Agilex 9's A-Tile. Inside the Agilex 9, the analog signals are routed to four 64 GSPS, 10-bit A/D converters.

The A/D digital outputs are delivered into the programmable logic and processor system for signal processing, data capture or for routing to other resources.

#### **D/A CONVERTER STAGE**

The Agilex 9's four D/A converters accept baseband real or complex data streams from the FPGA's programmable logic. The analog output of each of the 64 GSPS, 10-bit D/As is transformer-coupled to a coax connection located within a VITA 67.3C connector.

#### **CLOCKING AND SYNCHRONIZATION**

The DRF5580's Timing Bus Circuit can generate all required clocking needed to operate all features of the board. In addition, it can receive a 10 to 100 MHz reference clock from either an on-board synthesizer, the VITA 67.3C connector, or from the VPX-P1 sync bus interface. The Timing Bus Circuit includes a jitter cleaner and provides the reference clock and sync signals to the A-Tile Clock Generator. A multifunction gate/trigger input is also available on one of the VITA 67.3C connectors for external control of data acquisition and playback. For larger systems requiring multiboard synchronization, a multisignal sync bus interface is provided on the VPX P1 connector. These signals include the reference clock and all required complementary timing signals to provide synchronization across multiple boards.

#### MEMORY RESOURCES

The DRF5580 architecture supports 8 GBytes of DDR4 SDRAM memory accessible from the Programmable Logic. Userinstalled IP, together with the Mercury-supplied DDR4 controller core within the FPGA, can take advantage of the memory for custom applications. An additional 8 GByte bank of DDR4 SDRAM is available to the Quad-core ARM Cortex-A53 processor as program memory and storage.

#### 1, 10 AND 40 GIGE INTERFACE

The DRF5580 includes 1, 10 and 40 GigE interfaces for control and data transfers. These interfaces are independent of the optical 100 GigE interfaces. The 1 GigE interface provides a direct connection to the ARM processor.

#### **EXPANDABLE I/O**

The DRF5580 supports eight 25 Gb/sec full duplex optical lanes to the VITA 67.3C connector. With the built-in dual 100 GigE UDP interface or installation of a user-provided serial protocol, this optical interface enables a high-speed gigabit data streaming path between boards.

#### FLEXIBLE MODULAR DESIGN

While the DRF5580 follows the form factor of a standard 3U OpenVPX board, the unique modular design of the DRF2580 System on Module (SoM) provides the flexibility to deploy this solution in many different situations. The DRF2580 SoM contains all of the key components including the Agilex 9 FPGA, DDR4 SDRAM, and power and clock management.

In the case of the DRF5580, the SoM is mounted on a 3U OpenVPX carrier which complements the design with a timing bus circuit, analog signal conditioning, and an 8x 25 Gbps optical transceiver. As a module and carrier board set, the DRF5580 becomes a complete, ready-to-deploy 3U OpenVPX solution available for conduction-cooled SOSA aligned deployment.

The DRF2580 can also be mounted on other carriers available from Mercury to support standard form factors; or for applications that require a non-standard footprint, Mercury supports the module with a design kit for users to engineer and build their own custom carrier. As a complete and tested module, the DRF2580 encapsulates best-in-class electrical and mechanical design, eliminating some of the most challenging aspects of embedded circuit design and allowing the user to focus on the application-specific carrier design.

#### **EXTENDABLE IP DESIGN**

For applications that require specialized functions, users can install their own custom IP for data processing. Mercury's FPGA Design Kit (FDK) includes the board's entire FPGA design that can be edited using Intel's Quartus<sup>®</sup> Prime Software. For all supplied IP, all source code and complete IP core documentation is included. Developers can integrate their own IP along with the factory-installed functions or use the Mercury's BSP and FDK to completely replace the IP provided by Mercury with their own.

#### SPECIFICATIONS

#### Field Programmable Gate Array

Type: Intel Agilex 9 SoC FPGA AGRW014

#### Agilex 9 RF Signal Chain

Analog Inputs

- Quantity: 4

- Connector: VITA 67.3C

- Input Type: Transformer-coupled

A/D Converters

- Quantity: 4

- Sampling Rate: 64 GSPS

- Resolution: 10 bits

- Analog Outputs

- Quantity: 4

- Connector: VITA 67.3C

- Output Type: Transformer-coupled

- D/A Converters

- Quantity: 4

- Sampling Rate: 64 GSPS

- Resolution: 10 bits

- Reference Clock

- Source: Switchable between on-board synthesizer, external source, sync bus (used for multiboard sync)

- Connector Type: VITA 67.3C (for external source)

#### Gate/Trigger:

- Source: Programmable through software or external source

- Connector Type: VITA 67.3C (for external source)

- Level: LVCMOS

# Hard Processing System

ARM Cortex-A53:

- Quantity: 4

- Speed: Up to 1.5 GHz

Processor I/O:

- Interface: 1 GigE

- Location: VPX-P1

#### FPGA I/O

- Interface: GPIO

- Quantity: 11 Pairs

- Type: LVDS

- Location: VPX-P1

- Interface: 10 GigE

- Location: VPX-P1

- Interface: 40 GigE

- Location: VPX-P1

- Interface: Optical

- Quantity: 8 full duplex lanes

- Connector: VITA 67.3C

- Speed: 25 Gb/sec

- Laser: 850 nm

- Protocol: Factory-installed dual 100 GigE UDP IP cores provides greater than 24 GB/sec data transfers, other protocols supported with user installed IP

#### JTAG

Location: VPX-P0 or front panel

#### Memory

- Type: DDR4 SDRAM

- Quantity: 2 banks

- Size: (each bank) 8 GB; 72-bit

FPGA Configuration FLASH:

- Type: QSPI NOR Flash

- Size: 2 x 1 Gbit

#### Environmental

Option -763: L3 (conduction-cooled)

- Operating Temp: -40° to 70° C

- Storage Temp: -50° to 100° C

- Relative Humidity: 0 to 95%, non-condensing

Dimensions: VPX board

- Depth: 170.61 mm (6.717 in)

- Height: 100 mm (3.937 in)

- Weight: Approximately 14 oz (400 grams)

## **OpenVPX** Compatibility

The DRF5580 is compatible with the following module profile, as defined by the VITA 65  $\mbox{OpenVPX}$  Specification:

SLT3-PAY-1F1U1S1S1U2F1H-14.6.11-12

#### ORDERING INFORMATION

| Model   | Description                                                                   |

|---------|-------------------------------------------------------------------------------|

| DRF5580 | 3U VPX SOSA aligned 4-channel A/D and D/A board with Intel Agilex 9 Direct RF |

# mercury

# Corporate Headquarters

50 Minuteman Road Andover, MA 01810 USA +1 978.967.1401 tel +1 866.627.6951 tel +1 978.256.3599 fax

# International Headquarters Mercury International

Avenue Eugène-Lance, 38 PO Box 584 CH-1212 Grand-Lancy 1 Geneva, Switzerland +41 22 884 5100 tel Learn more Visit: mrcy.com/directrf Contact: mrcy.com/contact-us

The Mercury Systems logo is a registered trademark of Mercury Systems, Inc. Other marks used herein may be trademarks or registered trademarks of their respective holders. Mercury products identified in this document conform with the specifications and standards described herein. Conformance to any such standards is based solely on Mercury's internal processes and methods. The information contained in this document is subject to change at any time without notice.

© 2024 Mercury Systems, Inc. 1-1-120224-DS-DRF5580